an I-Connect007 publication

New SI Techniques for Large System Performance Tuning p.12

Signal Integrity Tools and Design Methodology in the Modern Age p.30

Much More!

## THE SIGNAL INTEGRITY ISSUE

THE best way to find a PCB fabricator, anywhere.

#### **DYCONEX AG**

Bassersdorf, Zurich, Switzerland

Contact Me

an MST company

Overview

Contact

Specs

About

Videos

**Photos**

**Brochures**

News

Based in Switzerland, DYCONEX AG has been in the printed circuit board (PCB) business for more than 40 years. The company is one of the true circuit board pioneers and the inventor of several outstanding manufacturing and substrate technologies. DYCONEX therefore has a well-earned reputation as being a technology leader, providing leading-edge solutions in flex, rigid-flex and rigid interconnects.

Markets: Communication, Industrial, Medical,

Military/Aerospace

Double-sided, Multilayer, Flex, Rigid-Flex, Other: **Board Types:**

Rigid

Mfg Volumes: Prototype, Small, Medium

Other Services: Consulting, R&D

3D Features, Blind/buried vias, Components, Filled/plugged via equential lamination, Sculpted f

nanagement

D 9001, MIL-P-50884, MIL-PRF-55110 mpliant, UL, Other: ISO 13485, variou

ndards, REACH Compliance

## Why YOU should Showcase:

- Capabilities listing for advanced search functionality

- Specialties and certifications listing

- Ability to upload brochures and videos

- Quick and easy "Contact" and "RFQ" buttons

- News, web and contact links

Click to see a partial list of registered OEMs!

www.thepcblist.com

## Profitability is more about leadership and management than any other factor.

Any business can be transformed quickly, easily and sustainably with the proven effective systematic methods we employ. For over 25 years, our clients have averaged a 300% ROI on this work. Returns of 1000% are not unusual, especially in early stages of implementation. Contact us today and get started on the path of doing the right things that allow growth and profitability to happen.

#### click to read

Learn more about the roadmap used to build great companies with a high level of profitability in this article from the March 2016 issue of **The PCB Magazine**.

For 25 years we have been doing Four New Agreements consulting and training, significantly improving businesses. This stuff really works!

—David Dibble

## **5100** Feature Content

# The Signal Integrity Issue

As the not-so-old saying goes, "If you don't have signal integrity issues yet, you will." This month we bring you a variety of SI articles, starting with our cover story by Michael Steinberger and Barry Katz of SiSoft, and Donald Telian of SI Guys. We also have feature articles by Dennis Nagle of Cadence Design Systems and Narayanan TV of Zuken, as well as a feature column by Abby Monaco of Intercept Technology. Finally, we have a great interview with American Standard Circuits' John Bushie.

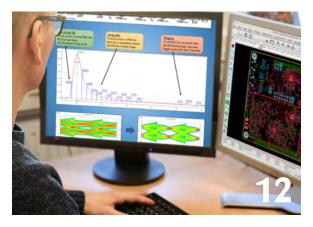

- 12 New SI Techniques for Large

System Performance Tuning

by Donald Telian, Michael Steinberger

and Barry Katz

- 30 Signal Integrity Tools and Design Methodology in the Modern Age by Dennis Nagle

- **42 Getting Signal Integrity Right by Design** *by Narayanan TV*

#### FEATURE COLUMN

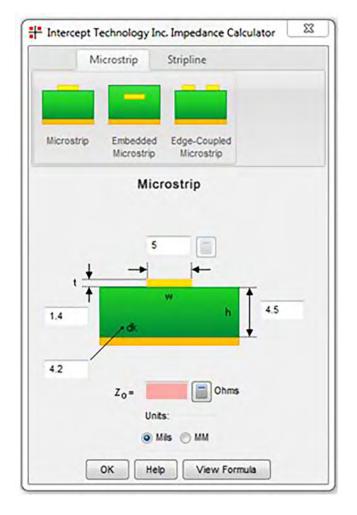

48 Having Fun With Impedance by Abby Monaco

## 185HR

## **High-Tg, Low-CTE Materials** with High Thermal Reliability

## **FEATURES**

- High Thermal Performance

- Tg: 180°C (DSC) (Base Laminate)

- ▶ Td: 340°C (TGA @ 5% wt loss)

- Low CTE for reliability

- T260: 60 minutes

- T288: >15 minutes

- Lead-free Compatible and RoHS Compliant

- UV Blocking and AOI Fluorescence

- High throughput and accuracy during PCB fabrication and assembly

- Superior Processing

- Closest to conventional FR-4 processing

- Industry Approvals

- ▶ IPC-4101D-WAM1 /98 /99/ 101 /126

- ▶ UL File Number E41625

- Qualified to UL's MCIL Program

- Core Material Standard Availability

- ▶ Thickness: 0.002" (0.05 mm) to 0.060"/0.062"  $(1.5 \, \text{mm})$

- Available in full size sheet or panel form

- Prepreg Standard Availability

- ▶ Roll or panel form

- ▶ Tooling of prepreg panels available

- Copper Foil Type Availability

- Standard HTE Grade 3

- ▶ RTF (Reverse Treat Foil)

- Copper Weights

- ½, 1 and 2 oz (18, 35 and 70 μm) available

- Heavier copper available upon request

- ▶ Thinner copper foil available upon request

- Glass Fabric Availability

- Standard E-glass

- Square weave glass fabric available

## **KEY APPLICATIONS**

- Heavy copper, 6 & 12 oz automotive applications

- Military

- Medical

- Industrial

#### ORDERING INFORMATION:

Contact your local sales representative or visit www.isola-group.com for further information.

**Isola Group**

3100 West Ray Road Suite 301 Chandler, AZ 85226 Phone: 480-893-6527 info@isola-group.com

Isola Asia Pacific (Hong Kong) Ltd. Isola GmbH Unit 3512 - 3522, 35/F

No. 1 Hung To Road, Kwun Tong, Kowloon, Hong Kong Phone: 852-2418-1318

info.hkg@isola-group.com

Isola Strasse 2 D-52348 Düren, Germany Phone: 49-2421-8080 info-dur@isola-group.com

## **July 2016**

Vol. 5, No. 7

thepcbdesignmagazine.com

#### **SHORTS**

- **A Little Impurity Makes** 10 Nanolasers Shine

- **Chemists Show New Way to** 40 Operate a Single Molecular **Swith**

- 47 **Quantum Processor for Single Photons**

- 51 Automotive LED Market Has a **Bright Future With the Rise of Replacement Products**

- 60 **Rechargeable Batteries That** Last Longer and Re-charge More Rapidly

- 77 From Battery Cell to Battery **Pack Components, Companies** are Seeking Better Margins

## **More Content**

### **ARTICLES**

- **Designing for Profitablility:** 68 Don't Over-Materialize Interview with John Bushie

- The Gerber Guide, Chapters 15 & 16 74 by Karel Tavernier

## COLUMNS

- We Want Your PCB Design Tips! 8 by Andy Shaughnessy

- The Rise of the Impedance Engineer 54 by Barry Olney

- 62 When Coatings Go Wrong by Phil Kinner

## HIGHLIGHTS

- 52 **PCB007**

- 66 MilAero007

- Top Ten PCBDesign007 **78**

### **DEPARTMENTS**

- 80 **Events Calendar**

- 81 Advertisers Index & Masthead

# BEST-IN-CLASS PRINTED CIRCUIT BOARDS FOR POWER ELECTRONICS

## 1. SOLUTIONS FOR HIGH CURRENTS

## **Heavy Copper Board**

• e.g. for AC/DC and DC/DC converter

## **Inlay Board**

• e.g. for start-stop systems

## 2. SOLUTIONS FOR HEAT DISSIPATION

#### **IMS Board**

• e.g. for LED headlights

#### **Cool Board**

e.g. for cell connectors and battery switches

## 3. SOLUTIONS FOR HIGH CURRENTS AND LOGIC ON JUST ONE PCB

### **Power Combi Board**

• e.g. for electrical pumps

## Smart p<sup>2</sup> Pack® (Power Embedding)

- e.g. for electrical motors

- low-inductance solutions

- improved electrical, thermal and EMC features

- miniaturisation due to new interconnect approach

## We Want Your PCB Design Tips!

## by Andy Shaughnessy

I-CONNECTO07

One of the most interesting things I've noticed about the PCB design community is that it's spread out among so many different segments of the electronics industry. You all work in a vertical occupation, but it's located across a very horizontal group of companies around the world.

As a result, PCB design information is often as spread out as PCB designers are. Fortunately, designers can now access design instruction through a variety of conferences, trade shows, and webinars. But there isn't really a centralized database for design information that's useful immediately—simple design tips that a designer can use on the next design.

We want to change that.

Soon, we'll be launching *Design Tips*, an ongoing feature that will be driven by input from PCB designers and design engineers. We want to hear from readers like you. Now is the time to make your voices heard.

Do you have a handy design technique that you utilize on almost every job? Did you discover a trick or two about your software that the rest of the design community might not be aware of? We want to hear these tips and so do your design colleagues.

Send us your favorite design tips, tricks and techniques. This information can encompass any area of PCB design or design engineering:

Find the ideal balance between Tx and Rx equalization settings up to

# 100x faster

SiSoft's new OptimEye technology helps you optimize your design faster so you can ship your designs faster!

- Replaces hundreds of blind sweep simulations with a single run

- •Designed specifically for AMI-based analysis

- •Generates custom per-channel equalization settings in a large system design

Evaluate OptimEye on your design today CLICK HERE TO GET STARTED!

www.sisoft.com

schematics, basic layout, placement, routing, materials, signal integrity, EMC, RF, hybrids, DFX, documentation, etc.

Keep your Design Tips entries short and sweet—no more than 100 words. Tool-specific tips are welcome, but keep them positive. We can't publish any tips anonymously; each tip will be published with your name, title and the name of your company. If you absolutely cannot use your company name, we'll need to have your city, state, or country if you're located outside the U.S.

We'll publish a new tip every few days, and readers will be able to see all of the previous tips as well. We see this as much more than a database; this will be a continuously updated knowledge base of useful tips that other designers can use immediately. After all, most designers know how to design a PCB. It's the little tricks that can help you save a few minutes here, and a few dollars there.

Now is your chance to share your knowledge with your colleagues, or just show off your great ideas. To submit your contribution to Design Tips, click here.

## The Signal Integrity Issue

This month, we focus on a topic that most of you have to contend with every day, or you will eventually: signal integrity. We have a variety of articles for your perusal, starting with our cover story "New SI Techniques for Large System Performance Tuning," a paper that was presented at DesignCon 2016. Authors Michael Steinberger and Barry Katz of SiSoft, and Donald Telian of SI Guys present some brand-new techniques for equalization tuning and discontinuity reduction in large systems—techniques that can improve your design margin. Dennis Nagle of Cadence Design Systems explains how a modern constraint-driven approach can enables all teams to get involved with signal and power integrity earlier in the process. Narayanan TV of Zuken discusses some common design mistakes that can affect signal integrity, and some new solutions that can address these issues.

Next, columnist Abby Monaco of Intercept Technology takes us on her journey to more fully understand the ins and outs of impedance. We also have a great interview with John Bushie of American Standard Circuits, who explains how PCB designers can avoid over-materializing their designs by utilizing solid design for profitability (DFP) methods.

We have some great content lined up for you over the next few months. And before you know it, it will be show time again. In the meantime, it's 90° here in Atlanta, which means it's time for some sweet tea. See you next month. **PCBDESIGN**

Andy Shaughnessy is managing editor of The PCB Design Magazine. He has been covering PCB design for 16 years. He can be reached by clicking <u>here</u>.

## A Little Impurity Makes Nanolasers Shine

Scientists at The Australian National University (ANU) have improved the performance of tiny lasers by adding impurities, in a discovery which will be central to the development of low-cost biomedical sensors, quantum computing, and a faster Internet.

Researcher Tim Burgess added atoms of zinc to lasers one hundredth the diameter of a human hair and made of gallium arsenide, a material used extensively in smartphones and other electronic devices. The impurities led to a 100 times improvement in the amount of light from the lasers.

Gallium arsenide is a common material used in smartphones, photovoltaic cells, lasers and lightemitting diodes (LEDs), but is challenging to work with at the nanoscale as the material requires a surface coating before it will produce light.

Previous ANU studies have shown how to fabricate suitable coatings.

The new result complements these successes by increasing the amount of light generated inside the nanostructure, said research group leader Professor Chennupati Jagadish, from the ANU Research School of Physics Sciences.

# We deliver Advanced PCB Solutions!

## **Landless Via Technology**

We're the only manufacturer in the world to have perfected a liquid photo-imageable resist (PiP) in electrolytic form, used for all our production.

**CLICK TO LEARN MORE**

Our unique processes enable us to create and deliver Advanced PCB Solutions that meet the needs of the demanding market at competitive prices!

## Fine line PCB, 2 mil line /space

We have developed a unique set of processes based on electro-depositable liquid photoresist.

**CLICK TO LEARN MORE**

## **Impedance Tolerance <5%!**

With our panel plating process combined with continuous foil lamination, our impedance tolerances are second to none!

**CLICK TO LEARN MORE**

CANDOR INDUSTRIES, INC.

**ADVANCED PCB SOLUTIONS**

by Donald Telian, SIGUYS, and Michael Steinberger, Barry Katz, SISOFT

This paper was originally published in the proceedings of DesignCon 2016.

#### **Abstract**

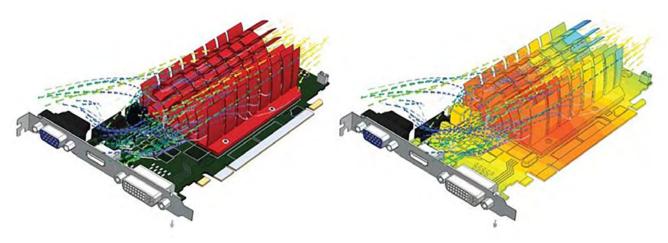

Large systems with multiple configuration options and extended product lifecycles provide performance tuning opportunities such as SerDes setting optimizations and manufacturing improvements. This paper describes newly-developed techniques for equalization tuning and discontinuity reduction, offering additional design margin. Cost reductions are also achieved as new signal integrity (SI) techniques demonstrate performance parity removing non-essential re-timers and PCBs layers. This is the fourth in a series of DesignCon papers detailing the design and implementation of a system characterized by multiple thousands of interconnected serial links spanning dozens PCBs, operating at 3rd and 4th generation serial link data rates (6 to 12 Gbps).

#### 1. Introduction

Simulation advancements released over ten years ago [1,2,3] allowed examination of serial links in greater detail, identifying performance limiters [4, 5] which motivated further refinements in the same [6]. Once tuned, the technologies were scaled to rapidly scan thousands of serial links to identify failure modes in rogue channels [7] enabling their correction and confident transition into production using simulated bit error ratios (BERs) as a qualifying metric [8]. This paper leverages and enhances these same technologies to provide large-system SerDes setting optimization and cost reduction, highlighting recent advancements in equalization optimization techniques and algorithms.

SerDes setting optimizations are applied to a wide range of channels across systems of various sizes. Optimization techniques are described, automated, applied to thousands of links and performance gains are quantified. SerDes tuning processes were simpler when one or two taps were available in the Tx and the Rx equalization options were few. However, with

## SILVER Lining...

Priced with the market

## COOLSPAN® TECA thermally & electrically conductive adhesive

COOLSPAN® TECA Film provides an easy solution to solving your thermal management challenges. Available directly from Rogers Corporation, without the middleman, COOLSPAN TECA is supported by Rogers' technical staff to help you gain the best result from this environmentally stable conductive adhesive. Keep your cool and maintain your budget.

- · Epoxy-based Adhesive Film

- · Market Priced to Silver Spot Price

- · Excellent Thermal & Electrical Properties

- · Predictable Flow

- · Durable & Reliable

SILVER MARKET PRICE

Advanced Connectivity Solutions

www.rogerscorp.com/COOLSPAN

Contact Rogers Corporation for more information or to request a sample USA - AZ, tel. +1 480-961-1382 • EUROPE - BELGIUM, tel. +32 9 235 3611

newer technologies the number of setting options grows exponentially as a larger number of Tx taps are available and trade-offs must be made between Tx and Rx equalization. As such, new tuning techniques are necessary. Furthermore, using re-timers to handle excessively long channels (40+ inches) seemed essential in previous generations of serial links. However as PCB and SerDes technologies continue to improve—combined with the optimization techniques described—we find that re-timers may not necessarily warrant their associated cost, complexity, and real estate.

Manufacturing improvements that enhance performance are also described. One example of a short connection with seven discontinuities spread across multiple PCB layers that initially showed multiple impedance changes in the 25% range is demonstrated to become nearly transparent over time. Relentless measurements on bare PCB fabrications, good vendor communication, and manufacturing process improvements and controls are key. Breakout traces longer than 1/4" should be compensated. However, intentional trace layout manipulation in the presence of impedance control and re-imaging during fabrication must be carefully managed. Dual-diameter via construction is shown to be a viable solution for reducing discontinuities when via lengths exceeds 200 mils, by using simulation confirmed by lab measurement to achieve 20% channel eye improvement in channels of various lengths. SI analysis also verifies

acceptable performance in reduced layer-count PCBs to achieve lower cost.

This is the fourth in a series of DesignCon papers from the authors, detailing the signal integrity analyses associated with a very large system design. The system is characterized by 7,000+ square inches of circuit board, multiple thousands of interconnected serial links spanning dozens PCBs, operating at 3rd and 4th generation serial link data rates (6 to 12 Gbps).

## 2. Performance Tuning Using SerDes **Setting Optimization**

This section illustrates system-level SerDes setting optimization performance tuning examples across large, medium, and small systems. For each system, baseline "coded" SerDes settings will be contrasted with "optimized" settings, where "coded" settings represent the previously best-known configuration for the SerDes based on previous simulation and hardware testing [4,7,8]. In other words, "coded" represents the settings coded into the system before optimized settings were derived.

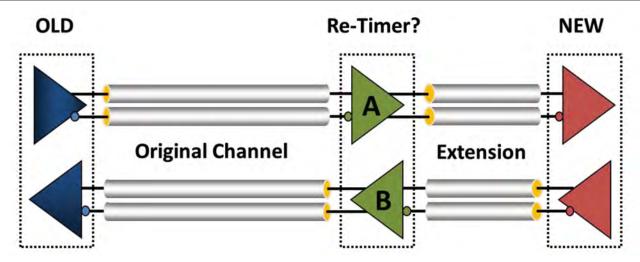

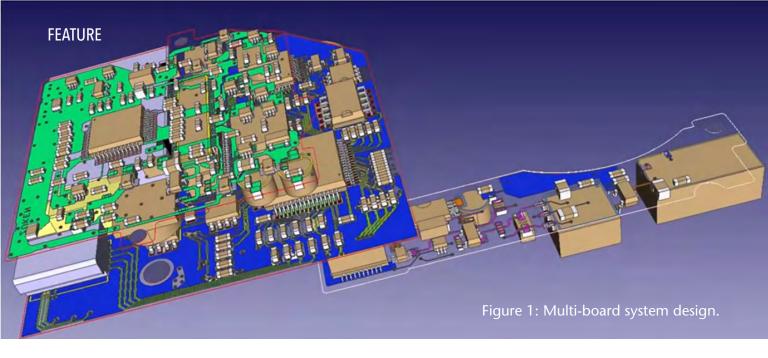

The system configuration examined required PCBs with newer SerDes technology to interoperate with PCBs using older SerDes technology, as shown in Figure 1. The system integration scenarios involved various connectors and modularity, not shown in Figure 1 for simplicity. As newer SerDes (red, at right) can compensate for additional loss, their PCBs typi-

Figure 1: System configuration combining serdes generations.

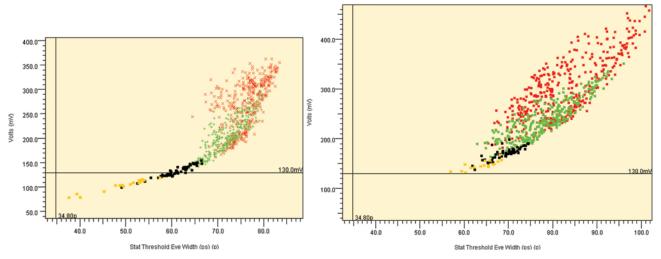

Figure 2: Simulated results, best-known settings (left), optimized settings (right).

cally include additional route length, marked in Figure 1 as an "Extension" to the "Original Channel" at left. This additional length raises the question of the need for re-timers (green, at center) when combined with older SerDes (blue, at left).

While the Tx in newer SerDes adds some new features, more significant changes have been made in Rx technology as CTLE (continuous time linear equalization) and DFE (decision feedback equalization) implementations continue to improve. As a result, it can be shown that the upper signal path in Figure 1 (old Tx driving new Rx) functions acceptably with the additional route length rendering the re-timers unnecessary in position "A." More challenging is the lower signal path (new Tx driving old Rx), thus reducing the design problem to assessing the need for the re-timer in position "B."

Since older technology is involved, real-time auto-negotiation of Tx settings in the physical system is not an option and other forms of channel optimization must be found. A design-time methodology, more fully described in the next section of this paper, is utilized to derive optimal performance given the available configurations and setting options in the SerDes involved. Specifically, the design task is to determine if the FFE (feed forward equalization) taps in the newer Tx can present an acceptable signal to the older Rx without the use of the re-timer in position

"B." This analysis is performed using the system model previously described in [7,8].

The first, and most challenging scenario examined was the largest system which included thousands of serial links interconnected across dozens of PCBs. The plot at left in Figure 2 shows simulated eye heights and widths for ~1,000 channels implemented without a retimer in position "B" versus design targets (horizontal and vertical markers). For this analysis, the channels were "coded" with best-known SerDes configuration settings. As shown, channels without the "extension" (red) perform acceptably against the targets, while some channels with the extension (green, with highlights in gold and black) are failing. Highlighted channels (gold and black) below and near the eye height target are those with the lengths up to 25% longer than initial budgets. Failures of such a linear nature are typically related to additional length and loss.

To address the failing channels, an initial implementation of channel optimization algorithms was tested with the results shown at right in Figure 2 (same color schemes). As shown, the performance of all channels exceeds design targets with more than 60% improvement in eye height and width for the worst-case channels. Performance comparisons revealed improvement in more than 85% of channels using these initial optimizations, motivating further refinements in the algorithms. Most importantly, Tx

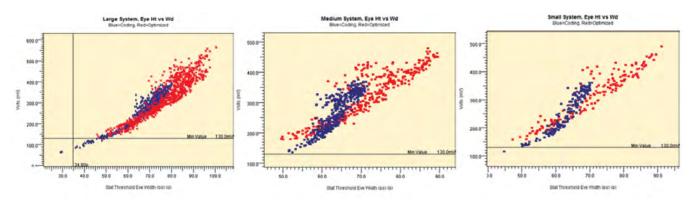

Figure 3: Default vs optimal eye openings for large, medium, and small systems.

Figure 4: Eye heights contrasted, original (left) and improved (right) optimization algorithms.

settings had been derived that moved channel performance within design targets for the worst-case channels (gold and black). The axes in Figure 2 are aligned for easier comparison.

As similar PCB/SerDes combinations were deployed in systems of differing scale, performance was examined for all scenarios. The plots in Figure 3 compare the eye openings using default SerDes coding (blue) against optimized coding (red) for three system sizes: large (left), medium (center) and small (right). These simulations add additional system-level jitter and improved optimization algorithms, and illustrate how optimization moves worst case channels within design targets (lower left corner, all plots) while providing improved margin for all channels.

For the largest system, Figure 4 shows optimization improvement by contrasting simulated eye heights using both the original algorithm (left) and the improved algorithm (right). Each point in the plots represents one channel. For each channel, the X axis plots simulated eye height using the original (baseline) SerDes cod-

# Engineering And Providing Balanced Interconnect Solutions

ing and the Y axis plots the eye height derived from the optimized coding. As such, points on the diagonal black line represent channels that performed the same using either SerDes configuration. Channels above the line have better eye heights using optimization, while points below the line represent channels with better eye heights using the baseline coding. The plots show that the optimized settings exceed the baseline in 85% of the channels using the original algorithm (left) and 95% of channels using the improved algorithm (right). As desired, worst-case channels in the lower-left corners of both plots increasingly move away from the black line. The Y axes are aligned to show ~100mV gain in some channels.

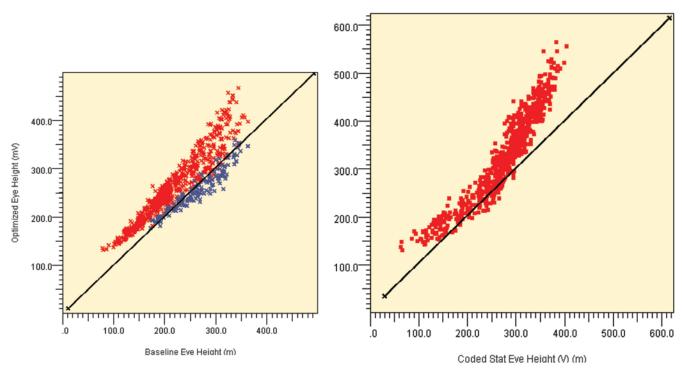

In both cases in Figure 4, the default (nonoptimized) coding is better in some mid-range channels. The channels highlighted in blue (left) represent channels that did not trade tap one optimally between the Tx and Rx in the original algorithm, as this trade-off is not simple to derive. Although the optimization techniques described in the next section will detail the removal of intersymbol interference (ISI) by forcing the pulse response to zero in pre- and post-tap UIs, in some cases that method does not provide the optimal result. In Figure 5, the

zeroforcing solution (blue) produces a smaller eye than the one derived by the refined automated algorithm (red). In some cases the complete elimination of ISI can remove too much amplitude from the main cursor (compare red and blue at ~8.25 nS). As such, optimization algorithms must intelligently trade-off amplitude, Tx/Rx taps, equalizable ISI, residual ISI in long tails, and other factors to arrive at the optimal solution. This is not a simple task—particularly since the "optimal" solution may vary depending on performance criterion.

## 3. System-Level Channel Optimization **Techniques**

#### 3.1 Overview

One of the tasks to be performed in the analyses shown in the preceding section was to optimize the combination of transmit and receive equalization separately for each channel in the system. Given the number of channels to be optimized, an automated procedure was required.

The optimization procedure we used is based on an analysis of the impulse response at the output of the receiver's IBIS-AMI model. The procedure is based on a pulse response derived from the impulse response and assumes

Figure 5: Pulse responses derived using conceptual and automated techniques.

that there are three equalization mechanisms applied to the channel:

- 1. Transmitter feed-forward equalization (FFE).

- The FFE is assumed to be a synchronously spaced tapped delay line with linear taps, in which the equalizing taps can occur either before or after the main tap.

- It is assumed that the maximum transmit voltage is constant, which is achieved by keeping the transmit swing constant and the sum of the absolute values of the taps equal to one.

- 2. Receiver continuous time linear equalization (CTLE).

- The CTLE is assumed to have a finite number of configurations which can be chosen through the IBIS-AMI model's input parameter string.

- No assumption is made concerning the relationship of one CTLE configuration to another.

- 3. Receiver decision feedback equalization (DFE).

- The DFE is assumed to be a synchronously spaced tapped delay line with linear taps, driven by the detected data.

- It is assumed that the detected data is almost always correct.

#### The overall procedure is

- 1. Define a starting configuration for the transmitter and receiver.

- 2. Solve for the impulse response of the passive interconnect network.

- 3. Apply the transmitter IBIS-AMI model to the channel impulse response, resulting in an impulse response at the input of the receiver model.

- 4. For each CTLE configuration:

- a. Set the receiver IBIS-AMI model to the selected CTLE configuration and apply the receiver model to the input impulse response.

- b. Using Hilbert space projection, compute the combination of FFE and DFE taps that will minimize the intersymbol interfer-

- c. Using Banach space techniques, adjust

- the FFE and DFE taps to maximize the eye height.

- d. Record the best eye height, CTLE configuration, FFE and DFE tap values.

- 5. Set the FFE taps in the transmitter IBIS-AMI model to the selected tap values and set the receiver IBIS-AMI model to the selected CTLE configuration. It is assumed that the receiver's DFE will perform its own adaptation.

- 6. If the FFE tap values have changed significantly since the last time they were set, go back to step 3 and repeat the optimization algorithm. If the FFE tap values have not changed significantly, execute the statistical analysis in the normal manner.

The procedure described was first implemented in a simplified form in 2002. While the initial approach was reasonably successful, the subsequent evolution has made the procedure much more complex and introduced a number of subtle details. These details, and the optimal automation of the same, are beyond the scope of this paper.

This paper will instead present techniques that system developers can apply manually to a pulse response in a waveform viewer either to obtain an equalization configuration that is close to optimum or to gain insight into the trade-offs that the optimization must address. The emphasis is on insight rather than automation.

The manual procedures to be described in subsequent sections are

- Clock recovery: The optimization procedure is critically dependent on the position of the recovered clock. An algorithm we call the "hula-hoop" algorithm quickly and accurately determines the average clock timing to be expected from a bang-bang clock recovery loop.

- Minimize intersymbol interference: Choose FFE and DFE tap weights that will minimize intersymbol interference, and understand how these choices will affect the eye height.

- Maximize eye height: Understand how minimizing the intersymbol interference improves eye height but does not obtain exactly the maximum eye height.

- CTLE vs. FFE trade-offs: The effect of CTLE can be very similar to the effect of FFE, often

# Geeka Palifization Za We're **stronger** in numbers!

Geek-A-Palooza is a social networking event for all of us electronics geeks that focuses on expanding our resources, building relationships and bringing every aspect of the local electronic industry together.

## **Our next event:** GeekaPalooza Boston | September 21

**Register Now!**

## Get your Geek on!

Boston

Thursday, September 21

**Register Now!**

Minneapolis

Thursday, October 13

**Register Now!**

## The Geeks Speak!

The event was great! The atmosphere seemed a bit more relaxed than a typical trade show. I noticed that those in attendance seemed more approachable than a typical trade show. Even those that I would consider "competitors" interacted a bit.

-Mike Brown, IDS

## Love to one of our sponsors!

PCB design specialists with a "Customer-First" approach and a never-ending commitment to quality.

With 200+ years of combined experience and expertise provided on thousands of printed circuit boards, you can be assured that your design will be done correctly, on time and within budget.

Visit their website

making the two mechanisms almost interchangeable. The low frequency gain of a given CTLE configuration determines how desirable that configuration is compared to a similar result obtained using FFE.

• FFE vs. DFE trade-offs: In some ways, the effect of DFE can be very similar to the effect of FFE; however, there are also some important differences that affect the way the two mechanisms should be used together.

### 3.2 Clock Recovery

An examination of the threshold crossing time distribution due to intersymbol interference for a number of different examples led to the conclusion that these threshold crossing time distributions are always symmetrical, or nearly so. This makes sense in that the effect of an intersymbol interference contributor on the transition time of a data edge is reasonably close to linear. That is, if a given intersymbol interference contributor delays the data transition by a specific amount when the interfering bit is a "one," then the data transition will be advanced by almost exactly the same amount when the interfering bit is a "zero."

Therefore the effect of all the interfering bits balances out (or nearly so) and both the median and mean transition times are determined by the primary transition from a "zero" in the preceding bit to a "one" in the bit to be detected, and back to a "zero" in the bit following the bit to be detected. In other words, the recovered clock timing will be half way between the transition times for a 010 data pattern in isolation.

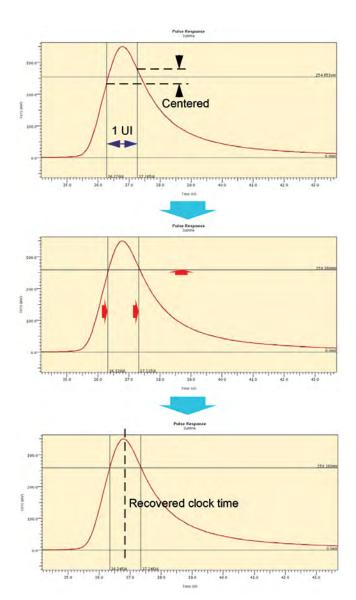

Equivalently, we can examine the pulse response, looking for two non-zero values which are exactly one bit time apart and equal to each other. The recovered clock will be half way between those two samples. We call this algorithm the "hula hoop" algorithm because if one imagines the pulse response to be a solid object (such as a length of bent wire) and one were to drop a ring with one UI diameter (the "hula hoop") on that object and level it, the center of the ring would be at the recovered clock time.

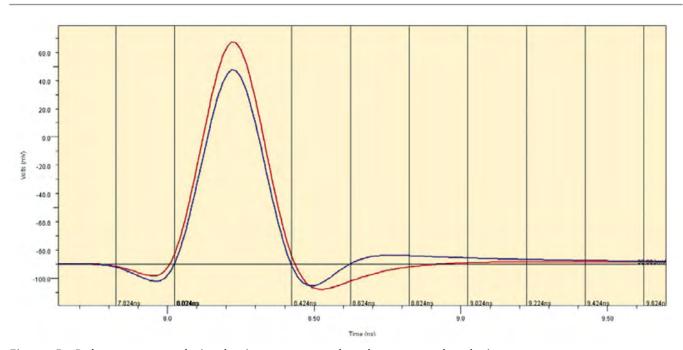

Figure 6 illustrates the procedure as applied in a waveform viewer. This procedure only takes a minute or two, and is quite precise.

Figure 6: Hula hoop algorithm as implemented in a waveform viewer.

- 1. The user starts by placing two vertical markers exactly one UI apart in a position that straddles the main pulse.

- 2. The user places a horizontal marker that is centered between the points where the vertical markers intersect the pulse response.

- 3. The user shifts both vertical markers to approximately the intersection of the horizontal marker with the pulse response, while keeping them exactly one UI apart.

- 4. Steps 2 and 3 are repeated until both the vertical markers and horizontal marker inter-

## Superior Quality Begins Here.

Since we first began in 1985, delivering the highest quality products possible has been our first priority. Our quality control systems are certified and we renew our commitment to quality each and every day.

Delivering quality products on time, combined with timely and accurate communication from our customer service team is how we create lasting relationships with our customers.

Take a look at our quality »

COMMERCIAL • MILITARY • MEDICAL • BAREBOARD

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

sect the pulse response while the vertical markers have remained one UI apart.

5. The recovered clock time is half way between the two vertical markers. This recovered clock time and times before and after that are an integer number of UI away are the times at which the intersymbol interference is to be evaluated.

#### 3.3 Minimizing Intersymbol Interference

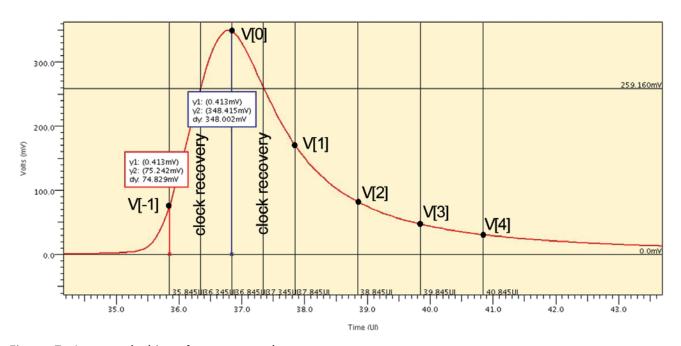

Given the recovered clock time, the next step is to choose FFE tap weights that minimize the intersymbol interference. Note that changing the FFE tap weights can affect the recovered clock time; so given the FFE tap weights that minimize intersymbol interference, it may be desirable to recover the clock time again and then fine tune the FFE tap weights. Figure 7 shows the same pulse response as in Figure 6, indicating voltage samples that are spaced an integer number of UI apart. The desired sample is V[0] and the remaining samples are intersymbol interference.

Since in a real data signal the adjacent bits can be either "zero" or "one," it's the absolute values of the intersymbol interference samples that matters. Assuming that the data signal is a balanced NRZ signal, the corresponding signal voltages are -0.5 and +0.5. The minimum eye height is then

$$V_{min} = V[0] - \sum_{i \neq 0} |V[i]|$$

(EQ1)

One of the most important characteristics of FFE is that the effect of an individual tap persists much longer than the time at which the tap was applied. Thus, when applying the manual procedure, it's important to apply the earlier FFE taps before the later ones because each tap affects the impact of subsequent taps.

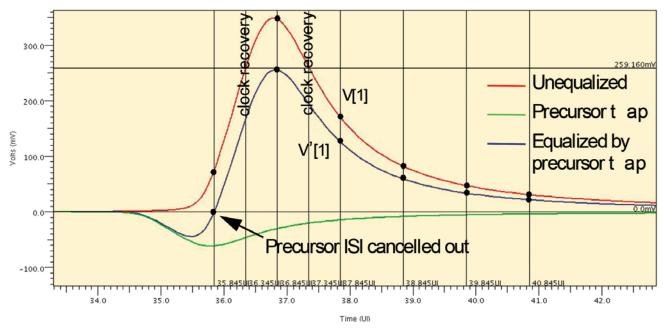

In the current example, the first tap is a single precursor tap. We will therefore determine its tap weight before addressing the postcursor taps. Suppose that the tap weight for the precursor tap is W[-1] and the tap weight for the main tap is W[0]. We have assumed that the sum of the absolute values of all the taps is one. Furthermore, we are assuming that the main tap is positive, and we can observe that the precursor tap is going to be negative. Therefore the tap weight constraint is

$$-W[-1] + W[0] = 1$$

(EQ2)

Figure 7: Intersymbol interference samples.

We also desire that the precursor tap should zero out the intersymbol interference at the precursor position. In other words, the signal contribution from the precursor tap at the precursor tap time (W[-1]V[0]) should cancel out the signal contribution from the main tap at the precursor tap time (W[0]V[-1]). Still keeping in mind that the main tap will be adjusting the amplitude of the main pulse, the desired condition is

$$W[0]V[-1] + W[-1]V[0] = 0$$

(EQ3)

Solving these ewo equations,

$$W[-1] = -\frac{V[-1]}{V[-1] + V[0]}$$

(EQ4)

$$W[0] = \frac{V[0]}{V[-1] + V[0]}$$

(EQ5)

Applying these equations to the values shown in Figure 7 produces the result shown in Figure 8. Note in Figure 8 that when the precursor tap response (in green) modifies the original pulse response (in red), the resulting pulse response (in blue) goes through zero at the precursor tap position. Note also that the amplitude of the main pulse has been reduced significantly, and that there was some equalization at the postcursor tap positions.

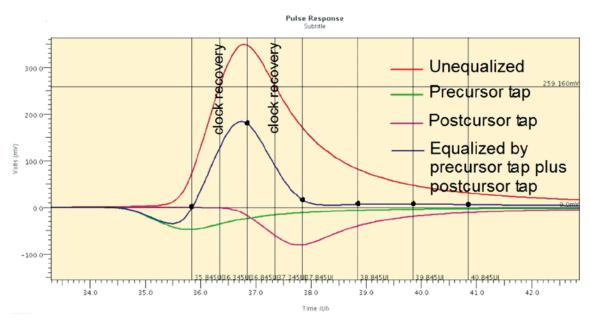

The calculation of subsequent tap weights follows the same process; however, the equations become much more difficult to solve algebraically. Note the voltage V'[1] measured at the first postcursor bit position in Figure 8. For the first postcursor tap, the equations are

$$W[-1] \approx -\frac{V[-1]}{V[-1] + V[0] + V'[1]}$$

(EQ6)

$$W[0] \approx \frac{V[0]}{V[-1] + V[0] + V'[1]}$$

(EQ7)

$$W[1] \approx -\frac{V'[1]}{V[-1] + V[0] + V'[1]}$$

(EQ8)

and the resulting pulse response is shown in Figure 9.

Figure 8: Pulse response with precursor tap applied.

Figure 9: Pulse response equalized by precursor tap plus postcursor tap.

Several observations can be made from Figure 9:

- 1. One could improve the equalization solution by increasing the magnitude of the post-cursor tap by a little bit. Note that when doing so, the other two taps would have to be adjusted as well, both to maintain tap weight normalization and to maintain good equalization at the precursor tap position.

- 2. The amplitude of the main pulse has been reduced by approximately a factor of two. This is one of the factors to consider when choosing FFE taps: equalization costs amplitude, reducing the energy delivered to the receiver.

- 3. The intersymbol interference at later symbols has been all but eliminated. This is especially true for a well behaved pulse response as shown in this example; however, the same phenomenon occurs for less well behaved pulse responses. In general, one FFE tap affects the intersymbol interference at multiple bit positions.

Equation 1 states that the minimum eye height is the main pulse response amplitude minus the sum of all the intersymbol interference amplitudes. FFE derives its effectiveness from the fact that even though it reduces the main pulse amplitude, it also reduces the intersymbol interference amplitude at many positions, thus

gaining leverage from the amplitude that was invested in equalization.

The general form of Equation 6 through Equation 8 can be applied to estimate additional tap weights. However, for best results those tap weights should be adjusted manually after the equations have been used to provide the initial estimate. The overall procedure can be completed in less than an hour—practical for a few test cases but not for equalizing thousands of channels in a system.

## 3.4 Intersymbol Interference vs. Eye Height

While minimizing intersymbol interference goes a long way toward improving channel performance, intersymbol interference as a performance measure is not the same as eye height or eye width. Furthermore, the optimum configuration for one performance measure will probably not be exactly the optimum for another performance measure. Rather, the optimum configuration will be a function of the performance measure that was chosen. This section will concentrate on eye height because it's almost always harder to maximize than eye width.

In the case of the FFE tap weight calculations described above, the weight given to the equalizing taps subtracts from the main pulse, and therefore subtracts from the eye height. Therefore backing off slightly from the tap weights

# Solve Challenges & Add Value with Traceability

## How does an effective traceability system impact manufacturing?

Find out with Brady's Traceability Whitepaper. This report explains:

- Cost, process and product quality improvements

- Why traceability is critical

- 4 key benefits of traceability

- Considerations for implementing a system

Visit

BradyID.com/trackingPCB

to download the

Traceability Whitepaper.

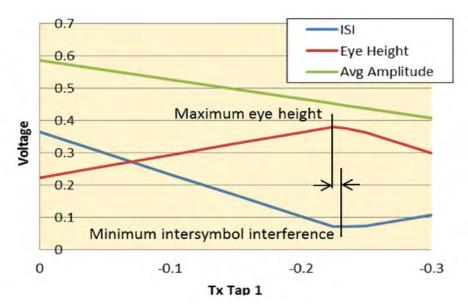

Figure 10: Trade-off between intersymbol interference and eye height for a single tap FFE.

for minimum intersymbol interference typically yields a slightly greater eye height.

Figure 10 is an example of the trade-off that can be expected for the case of a single tap FFE and a channel that is relatively easy to equalize. The green line is the average amplitude in the eye diagram at the receiver decision point, which is proportional to the main tap weight. The blue curve is the maximum intersymbol interference at the recovered clock time and the red curve is the minimum eye height at the recovered clock time. The red curve is equal to the green curve minus the blue curve (i.e., the average amplitude minus the intersymbol interference). In this case, reducing Tap 1 by a little over 4% increases the eye height by a little over 1%.

While more sophisticated algorithms are possible, for manual optimization it should be sufficient to reduce all of the equalizing tap weights in the FFE by a fixed percentage and add that amplitude to the main tap. It would be practical to evaluate the eye height for several different values of the fixed percentage; however, in most cases a value from 0% for channels that are difficult to equalize to about 5% for channels that are easy to equalize should be about right. PCBDESIGN

Due to the length of this article, we have published the remainder on the PCBDesign007 site. Click here.

**Donald Telian** is an independent signal integrity consultant with Si-Guys. Building on over 30 years of SI experience at Intel, Cadence, HP, and others, his recent focus has been on helping customers correctly imple-

ment today's multi-gigabit serial links. To contact him, click here.

Michael Steinberger, Ph.D., lead architect for SiSoft, has over 30 years of experience designing very high-speed electronic circuits. He is currently responsible for the architecture of SiSoft's Quantum Channel

Designer tool for high speed serial channel analysis. To contact him, click here.

Barry Katz, president and CTO of SiSoft, founded the company in 1995. As CTO, Barry is responsible for leading the definition and development of SiSoft's products. He has devoted much of his efforts at SiSoft

to delivering a comprehensive design methodology, software tools, and expert consulting to solve the problems faced by designers of leading edge high-speed systems. To contact him, click here.

| Key product features:                           | GF220 | GF265 | GF300 |

|-------------------------------------------------|-------|-------|-------|

| Consistent permittivity in high frequency range |       |       |       |

| Low Df at high frequency                        |       |       |       |

| Excellent thermal resistance                    |       |       |       |

| Low moisture absorption                         |       |       |       |

| Stable properties in high frequency range       |       |       |       |

**Learn more about SCGA-500 Series Materials**

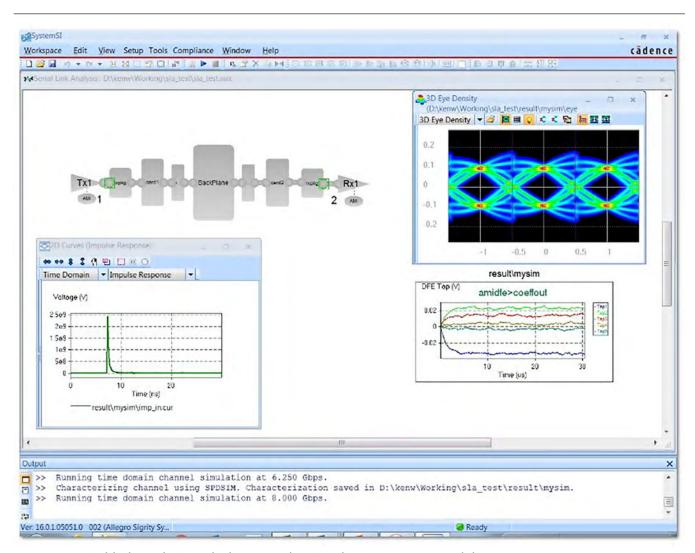

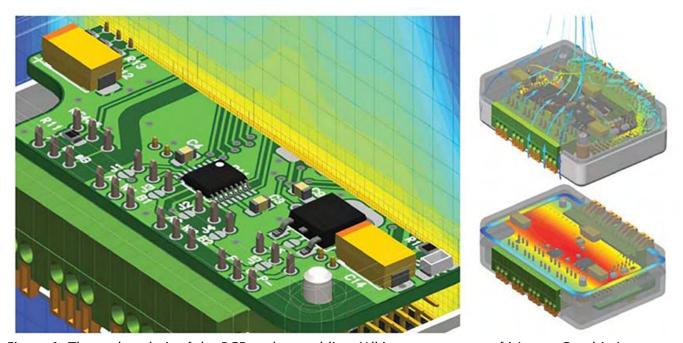

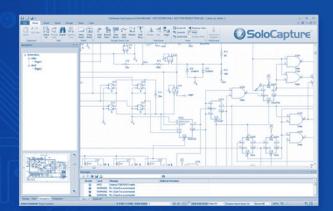

## by Dennis Nagle

**CADENCE DESIGN SYSTEMS**

The PCB design process has traditionally been done in silos. One group creates the design intent (schematic), another group implements the logic on the PCB, and yet another group does some checking of the design using analysis tools. This traditional approach has run into a number of problems.

The first problem was that prototypes were showing up in the lab that did not work due to complicated signal and power integrity problems not found by the analysis tools. But even when the analysis team equipped themselves with sophisticated analysis tools, the back-and-forth between silos or lack of time in the schedule tended to create chaos as design deadlines loomed.

Today, modern PCB design methodology offers a more team-oriented solution. With a front-to-back constraint driven approach that enables all groups to get involved with signal and power integrity, many potential problems are either avoided or found early in the design

process. With first order problems removed, the analysis team, with their sophisticated tools, is better positioned to focus on design sign-off so prototypes come back working the first time.

This article is focused on how each part of that design team can get out of their silo and work cooperatively. Using a common constraint manager, each group can utilize their varying levels of expertise to ferret out signal and power integrity problems.

#### **Pre-Layout**

For teams seeking to break out of their historic silos, tools can help by providing a certain amount of integration. One way that can happen is by having a constraint system integrated with your SI system at all stages of your design process. While decisions are being made for physical partitioning, component/IP selections, and power requirements, pre-layout analysis can help define your solution space and corresponding electrical constraints. This early analysis as part of a well-executed constraint driven flow saves time and prevents issues from propagating down to SI signoff.

## PCB fabrication, assembly, and free award-winning CAD design software.

Leading the industry for over 40 years as the preferred *prototype and production PCB solutions provider* for design engineers.

## **WE ALSO OFFER:**

- Best overall quality, value and competitive pricing

- Design for Manufacturability Tool: DFMplus

- Fully supported and free PCB123® design software

- Integrated assembly services

- FREE Ground Shipping

- PCBs as low as \$28 with ValueProto®

100%

On-time Guarantee

QUOTE NOW >

Questions? Comments? Suggestions?

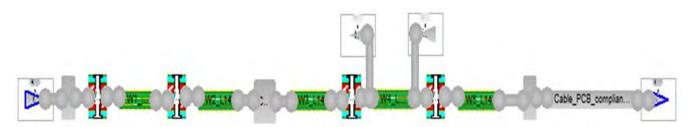

Figure 1: Pre-layout topology, with W-element and via models representing PCB interconnect.

Topology analysis is usually what comes to mind when thinking of pre-layout analysis and is an ideal environment for what-if analysis. Here you can start from scratch or by extracting nets from design data in the schematic or layout. In either case you can quickly build a representation of the major interfaces in the design. Models for active devices should be as accurate as possible and interconnect can be estimated or parameterized and swept.

Topologies that can be extracted from schematic and layout can allow all team members to access the same data for scheduling or constraint purposes. This can also enable design engineers to address reflection and topology issues along with the SI engineer. The topology can be used to drive scheduling of the nets for routing and placement and capture any other relevant constraints.

While a topology may be the first thing that comes to mind when thinking of pre-layout analysis, an often overlooked capability is that of virtual prototyping. This can be used to address situations where a netlist or design database isn't available when an SI engineer would like to create a specific prototype. Ideally, this would leverage existing design and library data for PCB layout such as stack-up, padstack, and footprints. These virtual prototypes can provide additional insight into placement and routing for simulations and constraint development that would not be possible with a topology. It is never expected to be a full representation of the design and can be extremely helpful in evaluating specific interfaces.

Whether topology or virtual prototype, both should be supported by structured device model management. Your SI models should get the same attention as schematic symbols and

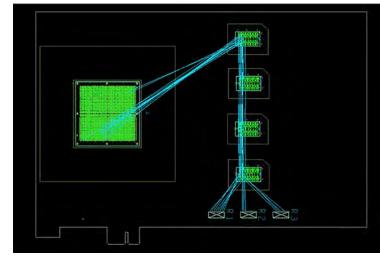

Figure 2: Virtual prototype of DDR3 interface with scheduling applied to address bus.

layout footprints. Analysis model management promotes reuse and saves setup time. Pre-layout analysis will identify cases where new models are needed which can then be validated and promoted to the central library. Even better is a process where the central library management system is fully integrated to include analysis models. This allows model assignments in the library data to track SI models as the design progresses from schematic to layout. Topology extraction from these design databases should support passing device models to the topologies.

## **Floorplanning**

While pre-layout analysis represents a starting point, floorplanning is where the actual physical layout starts to take shape. Pre-netlist floorplanning is where placement and form factor or other mechanical/thermal requirements are examined. But floorplanning should con-

Figure 3: Example of a design with nets represented in bundles to guide routing.

tinue once a netlist is ready and loaded into a layout-based application. This is really where design specific SI analysis can and should start even before any routing.

Why? There's an obvious goal of reducing the overall effort required for SI signoff and there's plenty that can be analyzed prior to the routing even starting. Let's take a look at what we typically concern ourselves with in the SI domain. We have signal quality with challenges like overshoot and ringback, timing-related issues like delay, what kind of routing topology works best for the situation and whether or not termination is needed, and of course crosstalk. The only one of these that absolutely requires routed traces in place is crosstalk.

This represents an ideal time to simulate the entire design, and in particular the interfaces that were not captured and simulated with topologies, for any of those SI issues, with the exception of crosstalk. Device model data assignments have propagated to the layout database as part of the netlist and simulating with unrouted nets will be quick since the interconnect is represented with a simple ideal model based

on Manhattan distance and an impedance. In some cases, the Manhattan distance can be replaced with design data to give a more accurate estimate of how certain nets will be routed. This can be useful at the pre-route stage to improve the accuracy of SI analysis.

Floorplanning stage analysis can lead you to placement edits or changes which are too painful after investing any time in routing. This is another example of where the constraint system and SI analysis leveraging the same design data can improve the overall process.

#### Screening

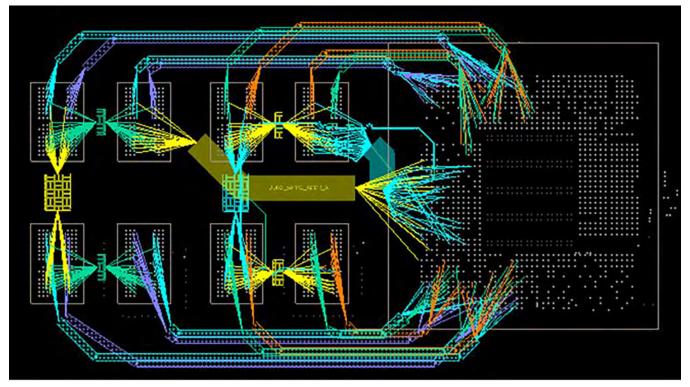

At this stage of the design, the focus is rule checking. Constraints and rule checking will drive any automated or manual routing with DRC violation feedback from the rules developed and implemented in the earlier stages. This traditional constraint-driven design methodology was born roughly two decades ago. Over the same time, data rates have gone from tens of Mbps to several Gbps for parallel interfaces plus we've seen the dawn of serial interfaces with even higher data rates. As a result,

DRCs now share the screening limelight with ERCs (electrical rule checks) and SRCs (simulated rule checks). As these names imply, they involve more than just traditional physical rule checks and rely on some of the same data we use for traditional SI analysis.

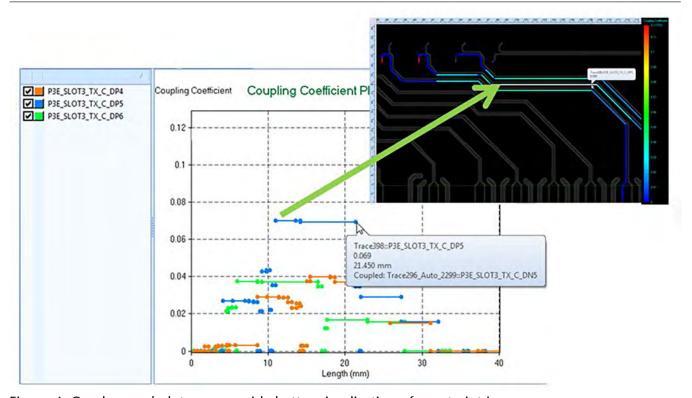

This represents an ideal time for the layout designer to catch as many potential SI issues before any post-layout analysis. Impedance and coupling can be checked and resolved without the need for any complicated setup or analysis. Results can be more than simple violation markers to provide better visual clues to violations and areas that need attention.

The most critical thing to consider for today's designs is how power and signal interaction affects signal integrity. As the design progresses and PDN structures such as planes are implemented, coupling among power nets, signals, and vias can and should be evaluated. Many constraints are formed at the early stages of a design before planes and vias exist. Performing physical rule checking as these elements are added should not be based on the assumption of ideal planes. Impedance, trace coupling,

crosstalk, delay, and skew need to account for the impact of power noise upon signals.

This new breed of SRCs performs analysis of signal and power coupling by applying a linear excitation to large number of signal nets. These SRCs report signal quality including all coupling noise while avoiding any time consuming non-linear simulation. The results guide layout designers to find issues general post-route rule checking, assuming ideal reference planes, cannot find. One example of this is where via coupling from a plane can induce crosstalk that increases as the traces are separated. This seems to violate not only common sense but also any traditional crosstalk rule that relies on ideal reference planes. It can only be captured when plane noise and via coupling are considered.

At this stage the device models assigned in the layout may not get exercised for each type of DRC, ERC, or SRC but it can be very advantageous if the same analysis engines and accurate solvers used for SI analysis can be accessed by the rule checking. We will examine some of these advanced engines in the next section.

Figure 4: Overlays and plots can provide better visualization of constraint issues.

## POWERED BY SCIENCE...

and Industry's

**Best Technical**

Team

USA

Al Gruenwald

John Meyers

Pat Valentine

Robert Coleman

Jon Bengston

Rich DePoto

Mark Eonta

## **Uyemura PCB finishes** are best in class...

... but our greatest strength is our technical team. UIC field and development specialists have an average of 26 years in the PCB industry, and a wealth of knowledge about how to make your shop succeed on all levels.

## **ENIG**

The industry standard for producing uniform mid-phos EN deposits with a thin topcoat of immersion gold, over copper. Solderable and aluminum wire bondable; no dummy plating.

### **ENEPIG**

Only UIC has multiple options - alloyed and non-alloyed palladium baths - so you can choose for highest stability, greatest speed, substantially improved diffusion layer for optimized corrosion protection, widest processing window.

## Via Fill Coppers

Including EVF-N, which simultaneously plates through-holes and blind vias (even those smaller than 150 μm), reducing process time by 50%.

www.uyemura.com

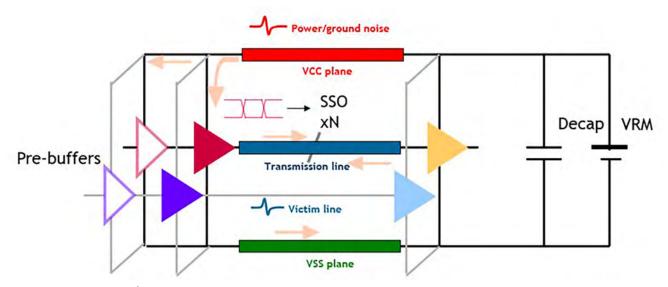

Figure 5: An SSN simulation.

#### **Detailed Simulation**

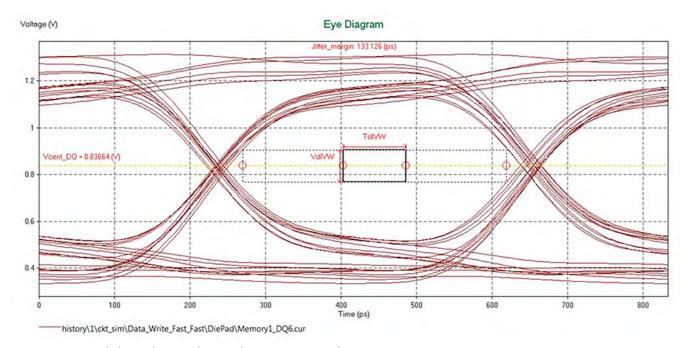

With the board-level screening passes completed, the design DRC-clean, and no significant reflection or crosstalk issues remaining, it is time to focus on the final stage of analysis. This typically involves detailed simulation to perform compliance analysis for the multi-gigabit interfaces in the design. These will commonly be DDR memory and serial link interfaces, with protocol-specific criteria to be evaluated.

Assuming analysis began in the pre-layout stage, this largely consists of performing detailed interconnect extraction of layout, replacing the "postulated" pre-layout W-element and via models with extracted S-parameters, and rerunning simulation/compliance checking for final design margins.

For today's DDR interfaces, the power distribution network (PDN) needs to be extracted along with the signals, to account for non-ideal power effects, such as simultaneous switching noise (SSN).

The most practical way to do this today is with a "hybrid" electromagnetic (EM) solver, which decomposes copper structures into vias, transmission lines, and shapes, solves them with application-specific solvers, and recombines the overall result into an S-parameter model. Including non-ideal power effects into DDR simulations prevents potential problems from being masked by ideal plane assumptions.

Figure 6: Signals assuming ideal power (top) vs. non-ideal power (bottom).

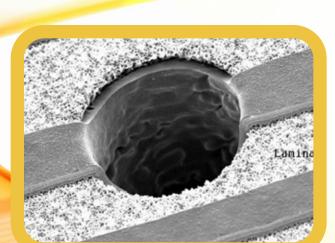

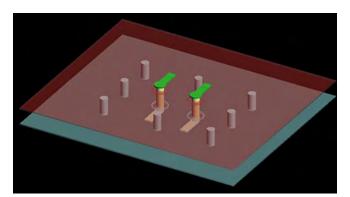

The extraction for high data-rate serial link interfaces must also be done with care and requires even high levels of accuracy. While uniform PCB traces can be modeled nicely with today's 2D field solvers, the via arrays used for layer transitions will usually require full wave 3D extraction for accurate representation.

Figure 7: 3D via array structure.

Those layer transitions often create the largest impedance discontinuities seen in the signal path, and play a key role in the accuracy of the overall channel model.

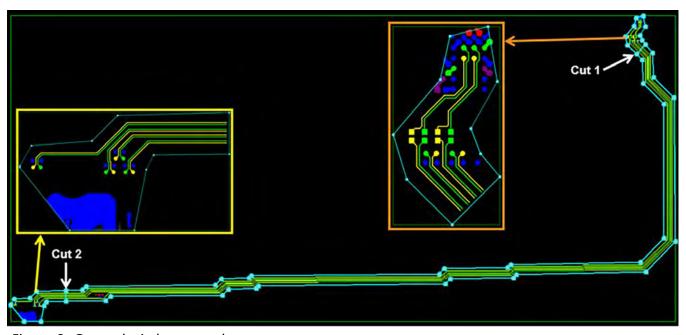

Full-wave 3D solutions are computationally intensive, and it can easily take several hours to extract a set of differential pairs coupled together. The 3D meshing done along the long uniform PCB traces is a significant culprit in the overall solution time, and is unnecessary for these largely 2D structures. A "cut-and-stitch" methodology can be used to focus the more expensive 3D field solution where it is warranted. while traditional 2D techniques can be used to quickly solve uniform transmission lines. This

"full wave where you need it" approach, combining multiple field solvers, can be automated by cutting out the serial link path from the overall design, breaking it up into "cutting zones," and designating those zones for the solver of choice. The project can be automatically broken down, solved in pieces, and re-combined into a composite S-parameter.

With accurate S-parameter extraction completed, pre-layout test benches can quickly be updated, incorporating the detailed interconnect models into the analysis.

Similar attention needs to be paid to device modeling. Multi-gigabit interfaces generally utilize equalization to achieve the required signal quality. Interfaces running over 10Gbps usually use adaptive equalization techniques, where the equalization behavior changes over a period of time. Traditional time step-based circuit simulation cannot run enough data traffic in order for the equalization to adapt, produce enough samples in the eye distribution, and enable bit error ratio (BER) to be extrapolated. These types of interfaces require channel simulation, which uses impulse response techniques to simulate high-capacity traffic. Channel simulation also enables IBIS-AMI device models to be used. These types of device models incorporate exe-

Figure 8: Cut and stitch approach.

cutable software modules, which can model the types of adaptive equalization commonly used today, such as continuous time linear equalization (CTLE), decision feedback equalization (DFE), and feed forward equalization (FFE).

While IBIS-AMI models are much more readily available for SerDes devices than just a few years ago, there may still be situations where an IBIS-AMI model is not available for a specific device, but you know the general characteristics of its equalization, such as the number of FFE taps or the CTLE frequency response. In these cases, today's tools enable you to quickly synthesize the IBIS-AMI model you need to carry out the simulation, and simulate your system-level interface.

With appropriate interconnect and device models in place, you can get down to the busi-

ness of verifying compliance for your critical high speed interfaces. For DDR interfaces, the landscape is changing. Starting with DDR4, memory interfaces are starting to adopt serial link modeling and analysis techniques. Memory controllers now have the FFE and CTLE techniques that serial links have had for many years, and because of that, are beginning to use IBIS-AMI models as well. In addition to device modeling, we now see standards like DDR4 moving from a traditional setup and hold time compliance approach to a mask-based one, like those historically seen for serial links, along with specific BER requirements.

Checking compliance for signal quality and mask adherence for entire memory interfaces full of signals (and even multiple interfaces in

Figure 9: Serial link analysis including equalization from IBIS-AMI models.

Figure 10: Mask-based compliance for DDR4 signals.

a design) can be very time-consuming, so good automation of waveform postprocessing is essential, along with generation of detailed sign-off reports.

In addition to the mask-based compliance checking above, serial link compliance will often have other unique requirements for the interface, including specific frequency domain characteristics for the interconnect.

In summary, thorough verification flows from good pre-layout analysis. Simulation test benches used up front can be re-used and updated with detailed interconnect models extracted from layout. Different types of EM solvers are needed to perform power-aware bus extraction for DDR interfaces, and intelligent deployment of full-wave techniques is needed to efficiently characterize layer transitions for high data rate serial link interfaces. Automated, interface-specific compliance analysis needs to be applied to the final design, allowing you to sign off your design to fabrication with confidence, and help achieve first-pass success in the lab.

| No.    | Parameter                                | Symbol                     |        |

|--------|------------------------------------------|----------------------------|--------|

| Chanr  | nel Tolerancing Eye Mask Values (tabl    | e 4-27 in PCI Express Base | spec.) |

| 1      | Eye Height                               | V <sub>RX-CH-EH</sub>      |        |

| 2      | Eye Width at Zero Crossing               | T <sub>RX-CH-EW</sub> 5    |        |

| 3      | Peak EH Offset from UI Center            | T <sub>RX-DS-OFFSET</sub>  |        |

| 4      | Range for DFE d <sub>1</sub> Coefficient | V <sub>RX-DFE-COEFF</sub>  |        |

| 5      | Eye Mask                                 |                            | V      |

| Differ | ential Insertion Loss (figure 4-66 in PC | I Express Base spec.)      |        |

| 6      | Insertion Loss                           | SDD21                      | V      |

| Differ | ential Return Loss (figure 4-56 in PCI   | Express Base spec.)        |        |

| 7      | Tx Return Loss                           | RL - Tx                    |        |

| 8      | Rx Return Loss                           | RL - Rx                    | V      |

| Stress | ed/Swept Jitter Test (figure 4-74 in P   | CI Express Base spec.)     |        |

| 9      | Stressed/Swept Jitter                    |                            | V      |

#### Channel Tolerancing Eye Mask Values

| Item                                     | Value<br>25 mV | Simulation Results                  |        | Pass Fail<br>Pass |

|------------------------------------------|----------------|-------------------------------------|--------|-------------------|

| Eye Height                               |                | V <sub>RN-CH-EH</sub> 68.572        |        |                   |

| Eye Width at Zero Crossing               | 0.3 UI         | T <sub>RX-CH-EW</sub> (UI)          | 0.361  | Pass              |

| Peak EH Offset from UI Center            | ±0.1 UI        | T <sub>RX-DS</sub> -<br>OFFSET (UI) | 0.062  | Pass              |

| Range for DFE d <sub>1</sub> Coefficient | =30 mV         | V <sub>RX-DFE</sub> -<br>COEFF (mV) | -0.006 | Pass              |

| Eye Mask                                 |                | Eye Mask                            |        | Pass              |

Figure 11: PCI Express Gen 3 compliance criteria.

#### **Conclusion**

Design engineers can create constraints and plan out bus routing. PCB Designers can quickly screen a design for both physical and electrical rule violations. And signal and power integrity engineers can run detailed simulations that they can count on as being highly accurate. While this may not sound like a new concept, there is now integration of analysis technology in the design environment that enables all members of the team to use the same underlying analysis capabilities with varying levels of detail and expertise.

Utilizing common libraries, common constraints, and common analysis engines makes

for a unique and highly communicative environment. No more silos! By enabling all members of the PCB design team to have a role in the electrical integrity of the design, fewer problems are found in the lab and fewer design iterations are required. This results in meeting time to market requirements and having a predictable schedule. **PCBDESIGN**

**Dennis Nagle** is a product engineering architect at Cadence Design Systems.

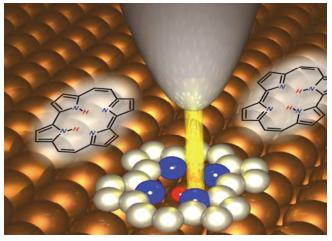

#### **Chemists Show New Way to Operate a Single Molecular Switch**

Researchers at the University of Liverpool are part of an international team that have shown a new way to operate a single molecular switch based on mechanochemistry.

In a study published in Nature Chemistry, the team which included Fritz-Haber Institute of the Max Planck Society (FHI-MPG), Berlin,

Donostia International Physics Center, San Sebastian and the Polish Academy of Sciences, showed how hydrogen atoms in a single organic molecule adsorbed on a surface can be switched in a controlled manner on a sub-molecular scale by the force from an atomically sharp, metallic tip.

This so-called tautomerization of hydrogen atoms is an important reaction in organic chemistry and molecular biology and is also a promising process for realizing single-molecule switches in molecular device applications.

In addition, by using chemically modified tips, this tip-induced process also provides a new strategy to gain a deeper atomistic insight into catalytic reactions and a new control of single-molecule chemistry.

Liverpool Chemist Professor Mats Persson said: "This research is a new finding in the field of mechanochemistry and has implications for the development of future nanotechnologies in particular molecular devices such as switches for molecular electronics."

Takashi Kumagai at FHI-MPG, who initiated

the study, wanted to explore the question of how much force is needed to operate a single-molecule switch. To address this, the researchers attached an organic molecule that exhibits tautomerization to a surface and approached the tip of a combined atomic force and scanning tunneling microscope within a few atomic distances above the molecule.

The research team also carried out extensive computer simulations in order to elucidate the atomistic mechanisms behind the force-induced tautomerization. Their calculations revealed that the tautomerization occurred by a reduction of its energy barrier upon approach of a metallic tip, while it could not be induced by a tip terminated by a Xe atom due to its inertness and softness.

# PCB Fab & Assembly Services from China's Experienced Manufa

More professional | More reliable | Quick turnaround | Less cost

### New Customer Offer Claim Now»

Save 15%, up to \$200 OFF Use Code: PCBDE007

#### **Our advantages -**

- ☑ Fully ISO9001:2008, UL and RoHS certified

- ☑ Pro-PCB fabrication up to 32 layers

- ☑ Prototype to production

- ☑ Min. tracing/spacing to 3mil/3mil

- ☑ Min. microvias to 0.1mm

- ☑ Special PCBs-Aluminum, Flex & Rogers PCBs, etc.

- ☑ Small Qty full turnkey PCB assembly

# Getting Signal Integrity Right by Design

#### by Narayanan TV

ZUKEN

As clock frequencies increase and active devices and interconnect traces shrink and are placed ever closer together, signal integrity (SI) becomes an increasing challenge. Today, SI is typically addressed late in the design process after the PCB layout has been completed by performing complex and time-consuming 3D extractions and simulations for high-speed lines.

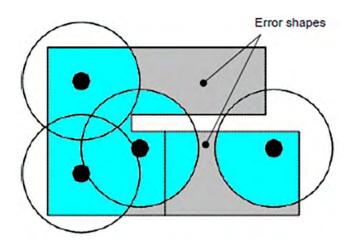

But with little attention being paid to SI during the layout process, the simulation frequently identifies numerous SI problems. Multiple design and simulation iterations are often required to resolve these issues, in some cases causing delays in bringing the product to market and increasing nonrecurring expenses. An embedded SI checker helps by automatically checking for common mistakes that frequently cause SI problems such as missing shielding, return path discontinuities, ground or power loops, impedance mismatches, etc. Even with this approach, simulations are still required as a final check, but reducing the number of issues that must be addressed at this late stage helps bring the product to market faster and reduces engineering costs.

#### SI Design Challenges

Increasing data rates, higher IO counts and greater design complexity are leading to greater challenges in meeting SI and electromagnetic interference (EMI) requirements. For instance, 3DIC technology utilizes through-silicon vias (TSVs) to eliminate bond wires and further reduce interconnection distance in stacked chip configurations, providing higher speed performance and lower power consumption at the cost of creating many new opportunities for harmful radiation. Meanwhile, regulatory authorities are tightening electromagnetic compatibility (EMC) requirements by requiring compliance at higher and higher frequencies. The trend towards integrating multiple radios each of which is an intentional radiator—into electronic products creates further challenges.

But the complexity of today's designs and the high levels of automation required to complete them in a reasonable time period usually prevent electrical designers from paying more than cursory attention to SI during the design process. Nearly all PCB design tools have builtin design rule checkers (DRCs) but they typically evaluate the design from a manufacturability perspective, rather than from an SI perspective. Simulation is normally performed after the design has been completed, when it becomes posMeeting the demands of the latest LED lighting designs delivering an unprecedented level of thermal performance

With the market need for ever-increasing thermal performance, the Ventec VT-4B family of thermally conductive IMS (Insulated Metal Substrates) deliver an unprecedented level of thermal performance through their established ceramic-filled halogen-free dielectric technology. Multilayered constructions are made possible through resin-coated foil and resincoated film options.

Contact us to discuss your requirements.

Ventec - wherever technology takes you, we deliver

#### Ventec International Group

179 Ward Hill Ave, Ward Hill, MA 01835, United States

T: 978-521-9700

E: ordersCA@ventec-usa.com

www.venteclaminates.com

sible to model its performance by calculating a 3D solution of Maxwell's equations, which provides an elegant mathematical representation of electromagnetic interactions. The result, all too often, is that large numbers of SI problems are identified at a point relatively late in the design process when changes are very expensive to make. As a general rule, the cost of design changes generally increases by an order of magnitude or more as the design moves from conceptual to detailed to simulation.

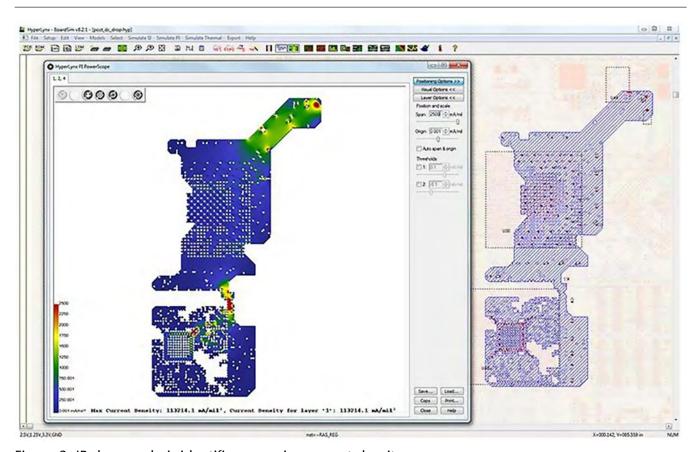

#### SI Checkers use Configurable Rules

The latest generation of PCB design solutions, such as Zuken's CR-8000, incorporate features like an SI checker in the form of EMC advisor that evaluates the design during the layout process to predict, analyze and control issues that may cause SI or EMC problems. An embedded field solver calculates characteristic impedance, unit length delays and the mutual inductances and capacitances between lines. The SI checker runs as a menu item without requiring external net or components lists, exchange files or translators. Users can configure each rule by assigning specific parameters to nets. This is important because every board design has its own unique tradeoffs between performance, cost and schedule, not to mention corporate culture.

The ability to configure rules enables users to take control over the process and adopt the rules to the needs of the specific project. The

user can weight rules so that some are considered more and others less important in the overall design rating. The user can also evaluate what-if scenarios by changing parameters globally and updating the rule checks. Files are provided to identify potential problems at the earliest stage possible in order to minimize the effects of design changes, reduce overall development cost, and speed up the design cycle.

#### **Common Design Mistakes**

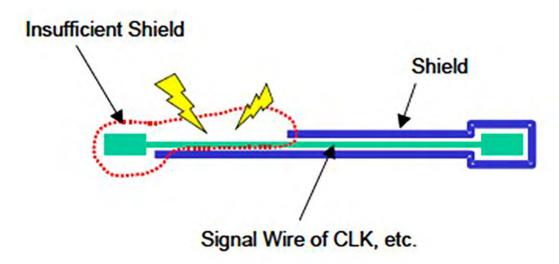

Shielding: Sensitive circuits such as clock and high-speed signal wiring often require shielding to protect them from nearby radio frequency (RF) fields. As an example, CE testing, which is required to sell products in the European Union, for example, typically subjects electronic products to a radiated field of 1 V/m to 10 V/m magnitude over a 80 MHz to 6 GHz frequency range. Some industries such as automotive and aerospace are required to withstand even more difficult tests. This RF energy may couple to sensitive circuits such as clock and high-speed signal wiring and induce voltages and currents that can adversely affect its performance. The SI checker inspects shields near applicable signal vias. When the shielded level is below the parameter set by the user, the design feature is called out. The rule checker recommends an appropriate remedy for each fault such as applying an appropriate shielding to the object net patterns, placing appropriate

Figure 2: Trace shielding check.

# Managing a global PCB supply chain can seem like a puzzle.

### Let us be the solution.

With over 35 years of experience and key partnerships around the world, we have what it takes to make your next project on time, on budget and hassle-free.

LEARN MORE ABOUT THE NUJAY SOLUTION D

shield vias near the applicable net vias and connecting the shields to ground or power.

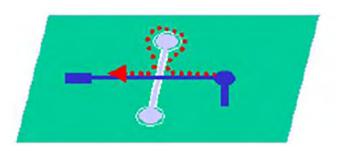

Return path discontinuity: Signal currents always take the path of lowest impedance, creating the potential for them to flow in unexpected directions, resulting in what is called return path discontinuity. When the return path forms a loop, the result may be increased delay in signal transmission or radiation that can interfere with other circuitry in the device or violate EMC regulations. The general rule of thumb is to minimize loop areas formed by return current for high-frequency signal, power and clock circuits. The SI checker identifies the target signal path, the wiring path connecting the target terminal pair, and the return path, the path closest to the target signal path between driver sound ground terminal and receiver side ground terminal. Next, the checker looks for an inappropriate return path, one that is not on the same layer or next layer as the return path or one that exceeds the permissible distance from the return path. The rule checker then calculates the severity of the loop based on the following formula: error rating = 1 - (errorpath length + return path length).

Impedance mismatch: Transmission lines become increasingly prone to noise as signal speed increases. In particular, mismatches between the trace's characteristic impedance and the driver's output or load's input impedance create signal reflections. These reflections in turn generate negative effects including radiation noise. Wiring width change is one of the factors that cause impedance mismatches. The SI checker calculates the characteristic impedance by finding the closest reference planes above and below the circuit. Wirings in the

Figure 3: Return path discontinuity check.

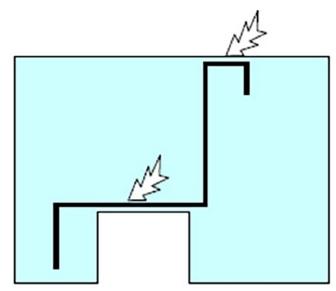

Figure 4: Trace near the plane edge.

Figure 5: Plane via distribution.

same layer are divided into sections and calculated separately when they have different reference planes.

High-speed signal wiring too close to the edge of a reference plane can also generate noise. The EMC advisor identifies wiring with frequency, rise time and voltage amplitude values that exceed user-specified parameters. Thus, the SI checker identifies potential risks for highspeed signals that may be prone to increased radiation noise.

Via density: If there are not enough vias distributed with sufficient density within any given area of a power or ground plane, the potential exists for this area to function like an antenna and generate unwanted radiation. In addition, lack of reference path vias may cause longer return loops and also contribute to increased simultaneous switching noise. The rule checker checks to see whether or not padstacks are distributed in the plane with sufficient density. It operates by marking off sections within a user-defined radius of the center of each via. The sections that have not been marked off are considered to be problematic and when the ratio of problematic to good sections reaches a specific level in an area, then that area is called out by the rule checker.

The SI checker also identifies many other mistakes that might be made in the design layout such as track resonance, EMC incompatible layer stack, isolated copper areas, overlapping power planes, high power plan impedance, etc. After running the selected rules, results are presented to the user in a graphical histogram. This also shows the results as a percentage performance rating and uses a custom color code to reflect the seriousness of the problem. Once the

rules have been run, the issues that have been detected can be highlighted in the PCB design. Complete control of the highlighting is available for any combination of rules and design items within the rules.

#### Conclusion